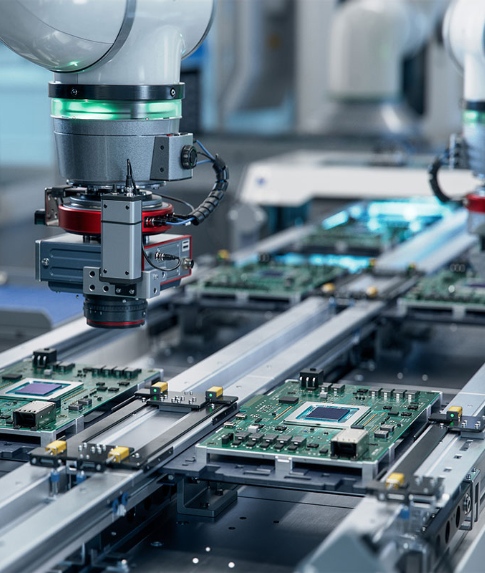

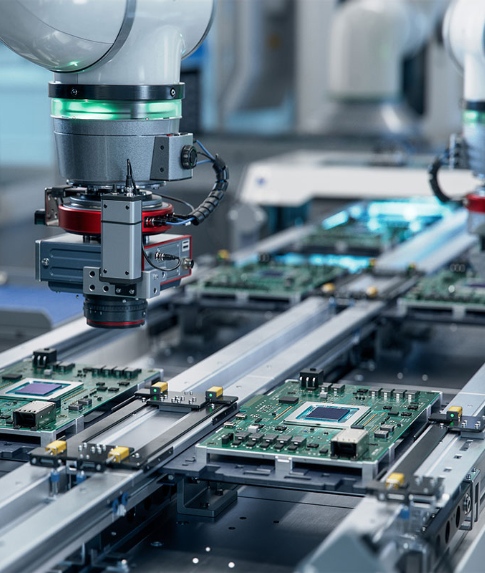

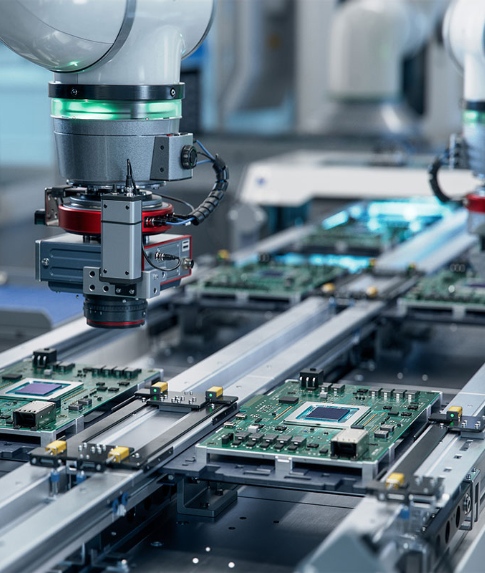

Die Grundlage der heute allgegenwärtigen intelligenten Geräte bildet eine kleine Leiterplatte (PCB), die das Wissen unzähliger Ingenieure und die Kristallisation präziser Technologie in sich trägt. Als Herzstück elektronischer Geräte integriert der PCB-Herstellungsprozess Materialwissenschaft, Präzisionsverarbeitung und Automatisierungstechnik. Dieser Artikel behandelt den Industriestandardprozess als Kernstück und analysiert die sieben Kernphasen der PCB-Herstellung, um Ihnen ein tiefes Verständnis der Präzisionsfertigung in dieser modernen Branche zu vermitteln.

1. Schemaentwurf

Entwerfen Sie mit Altium Designer, Cadence und anderen Programmen die Schaltungslogik. Durch DRC (Design Rule Check) wird sichergestellt, dass das Bauteillayout und die Verdrahtung den elektrischen Regeln entsprechen. Dabei müssen Signalintegrität, elektromagnetische Verträglichkeit (EMV) und andere Faktoren berücksichtigt werden. Optimieren Sie die Ausrichtung von Breite und Abstand. Beispielsweise müssen Hochgeschwindigkeitssignalleitungen nach dem 3-W-Prinzip (Leitungsbreite = 3-facher Leitungsabstand) ausgelegt werden.

2. Dateikonvertierung

Der Ingenieur erstellt (mit Grafikdaten für jede Schicht) Bohrdateien (Excel-Format) und Stücklisten als Produktionsanweisungen. Anschließend konvertiert er die Gerber-Dateien in Film und markiert die leitfähigen Bereiche mit schwarzer Tinte und die transparenten Bereiche auf dem nichtleitenden Substrat.

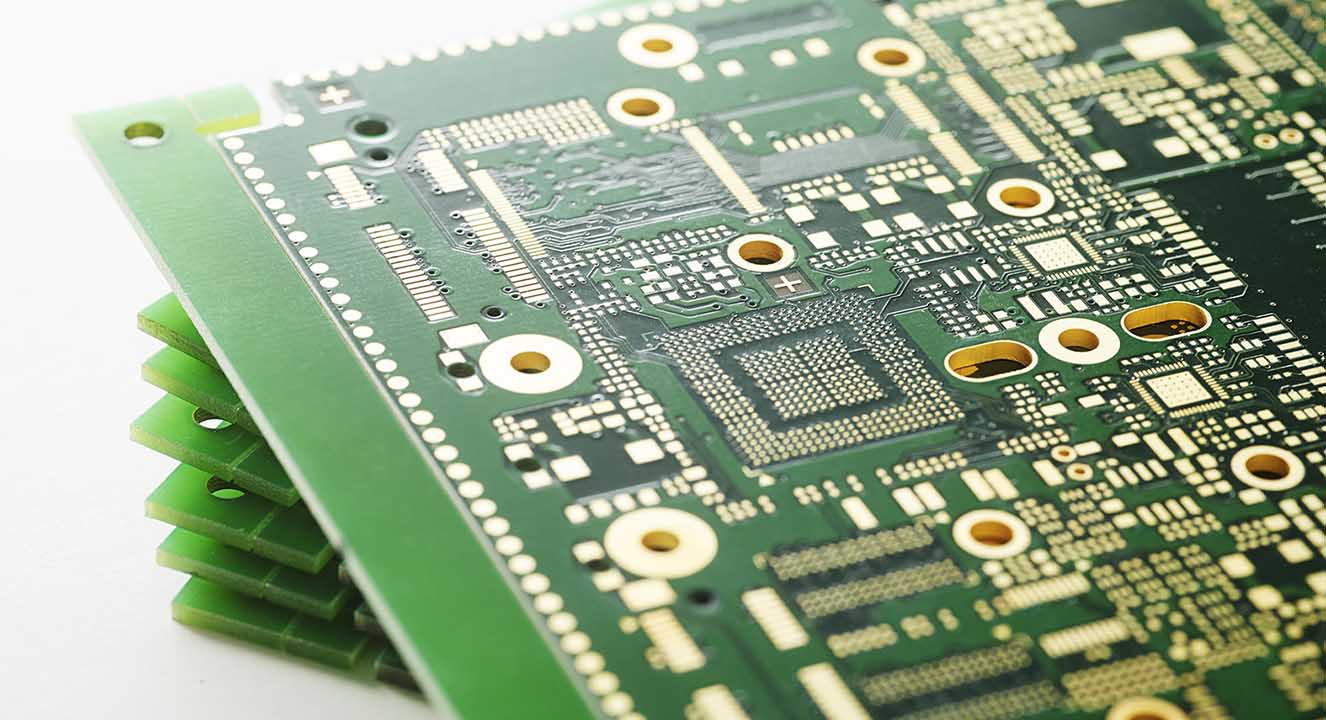

1. Substratauswahl

Üblicherweise wird FR-4-Epoxid-Glasfasersubstrat (Dielektrizitätskonstante 4,5–5,5) verwendet, während Rogers- oder Polytetrafluorethylen (PTFE)-Materialien für Hochfrequenzplatinen verwendet werden.

2. Laminierung schneiden

Die großen Platinen werden entsprechend der Auftragsgröße in Arbeitsplatten geschnitten. Die Fehlertoleranz beträgt ±0,1 mm, um die spätere Laminierungsausrichtung zu gewährleisten.

3. Oberflächenreinigung

Entfernung von Kupferoberflächenoxiden mit Plasmareiniger zur Verbesserung der Haftung der nachfolgenden Beschichtung.

1. Beschichteter Fotolack

Flüssige Fototinte wird gleichmäßig auf die Kupferoberfläche gesprüht und im Vakuum vorgebrannt, um eine feste Filmschicht zu bilden.

2. Belichtung und Entwicklung

Das Filmmuster wird mittels UV-Licht auf den Fotolack übertragen. Der Entwickler (Natriumcarbonatlösung) löst die unbelichteten Bereiche auf und erhält so das Schaltungsmuster.

3. Grafikbeschichtung

Eine 20–30 μm dicke Kupferschicht wird über den Grafikbereich plattiert, um die Leitfähigkeit zu verbessern. Eine selektive Verzinnung schützt die Linienkanten.

1. Säureätzen

Das vertikale Ätzen erfolgte mit FeCl₃- oder H₂SO₄+H₂O₂-Lösungen mit einer Geschwindigkeit von 0,5–2 oz/min. Die Linienbreitentoleranzen wurden auf ±0,02 mm kontrolliert.

2. Filmabziehen

Natronlauge entfernt Fotolackreste und legt die Kupferoberfläche im nichtleitenden Bereich frei.

3. AOI-Inspektion

Automatische Erkennung von Linienbreiten, Kerben und anderen Defekten mit einer 200-fachen Lupe.

1. Laminierungsprozess

Die Mehrschichtplatte wird mittels Hochtemperatur- und Hochdrucktechnologie eng mit der Isolierschicht verbunden. Das Prepreg (PP-Folie) füllt den Zwischenraum zwischen den Schichten, um die Leitfähigkeit zwischen den Schichten zu gewährleisten.

2. Laserbohren

Die präzise Bearbeitung von Mikrovias für High-Density-Interconnect-Platten (HDI) erfolgt mit einem Bohrer mit einem Durchmesser von nur 100 Mikrometern.

3. Mechanisches Bohren

Der schnell rotierende Bohrer steht in direktem Kontakt mit der Leiterplatte und entfernt das Material durch mechanisches Schneiden, um das gewünschte Loch zu erzeugen.

1. Chemische Kupferabscheidung

Eine dünne Schicht Kupfer wird chemisch auf die gebohrten, nichtleitenden Lochwände aufgebracht und dient als Unterlage für die anschließende Kupferbeschichtung. Dieser Prozess ist unerlässlich für die Herstellung elektrischer Verbindungen zwischen den Leiterplattenlagen und stellt einen wichtigen Schritt zur Gewährleistung der Gesamtleistung der Leiterplatte dar. Dieser Schritt erfordert eine Zirkulation und Filtration der Lösung, um Verunreinigungen zu vermeiden.

2. Auswahl des Oberflächenbehandlungsverfahrens

• HASL: Heißluft-Lötnivellierung (Schichtdicke 2–5 μm), kostengünstig, aber leicht oxidierend

• ENIG: Hochtemperaturbeständiges Chemisch-Nickel-Gold (Ni 3–5 μm/Au 0,05–0,1 μm), geeignet für hochdichte Pads

• Senksilber: ausgezeichnete elektrische Leitfähigkeit, jedoch nur 6 Monate lagerfähig.

3. Lötstopplackdruck

Durch Siebdruck oder LDI-Belichtung werden die nicht gelöteten Bereiche mit einer Lötstopplackschichtdicke von 10–30 μm abgedeckt.

1. Sichtprüfung

• Visuelle Inspektion: Mithilfe von Tageslicht oder speziellen Beleuchtungsgeräten verschaffen sich Prüfer mithilfe einer Lupe (in der Regel 5- bis 10-fach) einen umfassenden Überblick über die Leiterplatte. Sie prüfen insbesondere, ob Leitungen Kurzschlüsse aufweisen, ob Schutzschalter vorhanden sind, ob die Kupferfolie zerkratzt ist, ob freiliegendes Kupfer vorhanden ist und ob die Pads vollständig sind.

• Automatische optische Inspektion (AOI)

AOI-Geräte nutzen ein schnelles und präzises optisches Bildgebungssystem und Bildverarbeitungsalgorithmen, um Leiterplatten schnell per Laser zu scannen und Konstruktionszeichnungen zu vergleichen. Sie erkennen, ob Linienbreite und -abstand dem Designstandard entsprechen und ob Größe und Position der Pads korrekt sind.

2. Elektrische Leistungsprüfung

• Flying-Probe-Test: Durch Kontakt der beweglichen Sonde mit dem Testpunkt auf der Leiterplatte werden Leitungsein-/ausschalten, Widerstand, Kapazität und andere Parameter gemessen, um die Konnektivität zu überprüfen.

• In-Circuit-Test (ICT): Umfassende Tests von Bauteilen und Schaltungen auf Leiterplatten werden durchgeführt, indem Prüfspitzen über eine Stiftbettvorrichtung an bestimmten Prüfpunkten der Leiterplatte befestigt werden.

3. Impedanzprüfung

TDR-Geräte prüfen Hochgeschwindigkeits-Signalkarten (±10 % Toleranz), indem sie ein Impulssignal an die Übertragungsleitung der Leiterplatte senden und das reflektierte Signal analysieren, um die Impedanzeigenschaften der Übertragungsleitung zu bestimmen.

4. Röntgeninspektion

Dient zur Erkennung von Defekten im Inneren der Leiterplatte, wie z. B. dem Füllen von Sacklöchern oder vergrabenen Löchern, sowie zur Überprüfung von Brüchen, Kurzschlüssen und anderen Problemen in den internen Leitungen und zur Beurteilung der internen Qualität von BGA-Pads.

Von der Designdatei bis zur Auslieferung des fertigen Produkts durchläuft eine Leiterplatte über 200 Prozesse, wobei die Präzisionsfehler jedes Prozesses im Mikrometerbereich kontrolliert werden müssen. Mit der kontinuierlichen Weiterentwicklung von Wissenschaft und Technologie,die Leiterplattenfertigung entwickelt sich hin zu höherer Dichte, kleinerer Öffnung und mehr Umweltfreundlichkeit. Das Verständnis und die Beherrschung dieser Kerntechnologien, um mit der Zeit Schritt zu halten, ist für jeden Leiterplattenhersteller unerlässlich. Bei Fragen zur Leiterplattenfertigung kontaktieren Sie uns gerne. Wir bieten Ihnen einen umfassenden Service.

Email: sales@dqspcba.com

Unsere Stunden

24H